Intel has started shipping its next generation of Field Programmable Gate Arrays (FPGAs), a powerful form of highly customisable silicon that is being increasingly widely used in data centres and by hyperscale cloud service providers.

Claiming a 40 percent performance on its existing Intel Stratix 10 FPGAs, the chip maker said that the Agilex product family, its first 10nm FPGA effort, is landing with early access customers this week, including Microsoft.

The FPGAs can support up to 40 teraFLOPS of digital signal processor (DSP) performance (FP16 Configuration), with each Intel Agilex DSP block performing two FP16 floating-point operations (FLOPs) per clock cycle.*

Read this: Industry-First Xilinx Accelerator Card Runs in “Any Server, Any Cloud” – Fits Standard PCIe Slots

“Microsoft has been working closely with Intel on [Agilex development] and we are planning to use them in a number of upcoming projects,” said Doug Burger, technical fellow, Azure Hardware Systems at Microsoft.

He added: “We look forward to continued collaboration with Intel to deliver high-quality cloud services, big data analytics and ultra-intelligent web search results.”

The release follows hot on the heels of FPGA rival Xilinx, which started shipping its own latest “Versal” architecture two months ago (dubbing it an “adaptive compute acceleration platform” (ACAP) rather than a pure FPGA.)

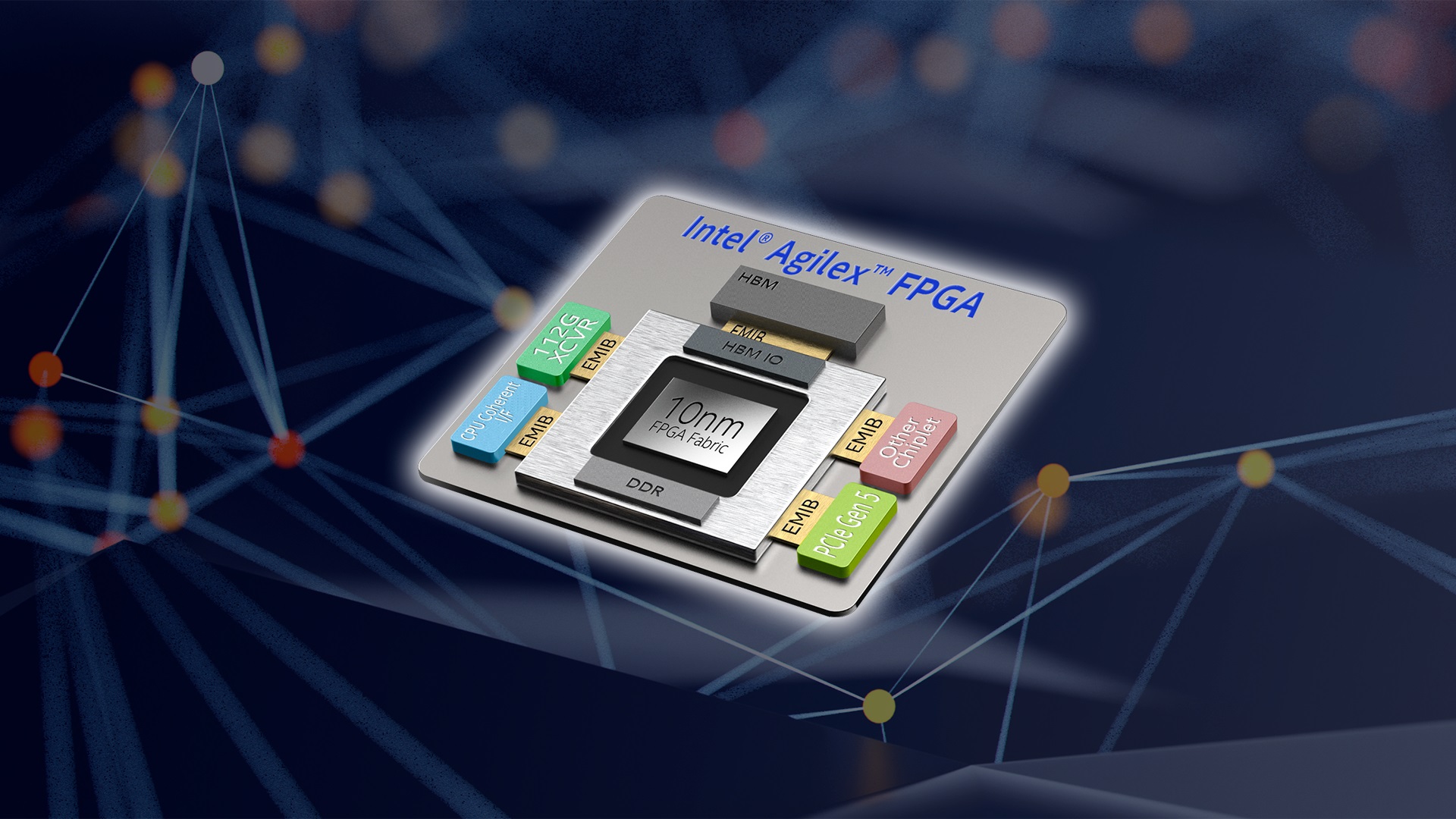

Intel said the architecture features innovations including support for the upcoming Compute Express Link (CXL), a high-speed CPU interconnect; PCIe Gen 5 interconnects; support up to 112 Gbps data rates for high-speed networking requirements and support for upcoming DDR5, HBM and Intel Optane DC persistent memory.

Intel FPGA Design: Quartus Prime Software , with “One API” Pending

The semiconductors can be designed using Intel’s Quartus Prime Design Software.

Intel continues to work on its “One API” project meanwhile: a programming model and portfolio of developer tools that aim to make it easier to map software to hardware; something that has historically been challenging for developers in the FPGA space.

Read this: If Moore’s Law’s Dead, What Now for Silicon Valley? The CEOs of Arm, Micron, Xilinx Have their Say

Intel hopes it provide a simpler way to programme its architectures, which span scalar (CPU), vector (GPU), matrix (AI) and spatial (FPGA) and currently require individual code bases, multiple programming languages and different tools/workflows.

A beta release of One API is expected in Q4. It will use the new direct programming language, Data Parallel C++ (DPC++), an open, cross-industry alternative to single architecture proprietary languages that looks set to be a hybrid of C++ and SYCL, Khronos Group’s high-level programming model based on OpenCL.

The “One API” project is designed to simplify the programming of diverse computing engines across CPU, GPU, FPGA, AI and other accelerators. It includes a portfolio of developer tools for mapping software to the hardware. A public project release is expected to be available in 2019.

Read this: Intel Unveils New Architectures: Open API, 3D Stacking, More

*DSPs, GPUs, and FPGAs serve as accelerators for the CPU, providing both

performance and power efficiency benefits. The accepted method to compare performance across them is to measure floating-point operations per second (FLOPS), where a FLOP is defined as either an addition or multiplication of single (32 bit) or double (64 bit) precision numbers in conformance with the IEEE 754 standard)